Table of Contents

Advertisement

Quick Links

Microprocessors and Memory

Technologies Group

Integrated Multiprotocol Processor

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different

applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not

convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in

systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the

Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended

or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all

claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with

such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and

are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Literature Distribution Centers:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912, Arizona 85036.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate,

1995 Motorola, Inc. All Rights Reserved

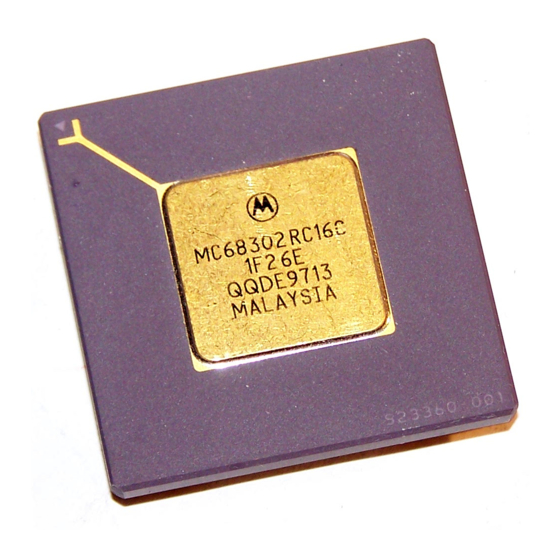

MC68302

User's Manual

Advertisement

Table of Contents

Summary of Contents for Motorola MC68302

- Page 1 Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages.

- Page 2 MC68302 USER’S MANUAL MOTOROLA...

- Page 3 Processor Product Brief . The MC68302 Integrated Multiprotocol Processor User’s Manual describes the program- ming, capabilities, registers, and operation of the MC68302; the MC68000 Family Program- mer’s Reference Manual provides instruction details for the MC68302; and the MC68302 Low Power Integrated Multiprotocol Processor Product Brief provides a brief description of the MC68302 capabilities.

- Page 4 JAPAN, Tachikawa 81(0425)23-6700 HYBRID COMPONENTS RESELLERS JAPAN, Tokyo 81(03)3440-3311 Elmo Semiconductor (818) 768-7400 JAPAN , Yokohama 81(045)472-2751 Minco Technology Labs Inc. (512) 834-2022 KOREA , Pusan 82(51)4635-035 Semi Dice Inc. (310) 594-4631 KOREA , Seoul 82(2)554-5188 MC68302 USER’S MANUAL MOTOROLA...

-

Page 5: Table Of Contents

Exception Vectors ................... 2-8 2.4.2 Exception Stacking Order ............... 2-9 Interrupt Processing ................2-11 M68000 Signal Differences ..............2-11 MC68302 IMP Configuration Control ............ 2-12 MC68302 Memory Map................. 2-14 Event Registers..................2-19 Section 3 System Integration Block (SIB) DMA Control.................... 3-2 3.1.1... -

Page 6: Paragraph Title Page

Timer Capture Registers (TCR1, TCR2)..........3-39 3.5.2.4 Timer Counter (TCN1, TCN2)..............3-39 3.5.2.5 Timer Event Registers (TER1, TER2)............3-39 3.5.2.6 General Purpose Timer Example............3-40 3.5.2.6.1 Timer Example 1..................3-40 3.5.2.6.2 Timer Example 2..................3-40 3.5.3 Timer 3 - Software Watchdog Timer ............3-41 MC68302 USER’S MANUAL MOTOROLA... - Page 7 Command Set ..................4-5 4.3.1 Command Execution Latency ..............4-7 Serial Channels Physical Interface............4-7 4.4.1 IDL Interface..................4-11 4.4.2 GCI Interface ..................4-14 4.4.3 PCM Highway Mode................4-16 4.4.4 Nonmultiplexed Serial Interface (NMSI) ..........4-19 MOTOROLA MC68302 USER’S MANUAL...

- Page 8 4.5.11.13 UART Mode Register................4-56 4.5.11.14 UART Receive Buffer Descriptor (Rx BD) ..........4-57 4.5.11.15 UART Transmit Buffer Descriptor (Tx BD)..........4-61 4.5.11.16 UART Event Register................4-63 4.5.11.17 UART MASK Register................4-65 4.5.11.18 S-Records Programming Example ............4-65 4.5.12 HDLC Controller..................4-66 viii MC68302 USER’S MANUAL MOTOROLA...

- Page 9 DDCMP Transmit Buffer Descriptor (Tx BD)........4-112 4.5.14.12 DDCMP Event Register............... 4-114 4.5.14.13 DDCMP Mask Register ............... 4-115 4.5.15 V.110 Controller .................. 4-115 4.5.15.1 Bit Rate Adaption of Synchronous Data Signaling Rates up to 19.2 kbps..................4-116 MOTOROLA MC68302 USER’S MANUAL...

- Page 10 SMC1 Transmit Buffer Descriptor ............4-142 4.7.4.3 SMC2 Receive Buffer Descriptor ............4-142 4.7.4.4 SMC2 Transmit Buffer Descriptor ............4-143 4.7.5 SMC Interrupt Requests ..............4-143 Section 5 Signal Description Functional Groups..................5-1 Power Pins....................5-2 Clocks ......................5-4 System Control ..................5-5 Address Bus Pins (A23–A1) ..............5-7 MC68302 USER’S MANUAL MOTOROLA...

- Page 11 Data Bus Pins (D15—D0) ............... 5-7 Bus Control Pins..................5-8 Bus Arbitration Pins................5-10 Interrupt Control Pins ................5-11 5.10 MC68302 Bus Interface Signal Summary ..........5-12 5.11 Physical Layer Serial Interface Pins............5-13 5.12 Typical Serial Interface Pin Configurations ........... 5-14 5.13...

- Page 12 D.1.3 Memory Interface ..................D-4 D.1.4 Memory Circuit..................D-4 D.1.5 Memory Timing Analysis................. D-4 Switching the External ROM and RAM Using the MC68302 ....D-5 D.2.1 Conditions at Reset................. D-5 D.2.2 First Things First ..................D-5 D.2.3 Switching Process................... D-6 MC68302 Buffer Processing and Interrupt Handling ......

- Page 13 D.6.13 Additional IMP To S/T Chip Connections ..........D-39 D.6.14 Initialization of the MC145475 ...............D-40 D.6.15 MC145554 CODEC Filter..............D-41 Interfacing a Master MC68302 to One or More Slave MC68302s ..D-41 D.7.1 Synchronous vs. Asynchronous Accesses..........D-43 D.7.2 Clocking....................D-43 D.7.3 Programming the Base Address Registers (BARs).......D-43 D.7.4...

- Page 14 Synchronous UART................D-67 D.8.13 SCP as a Transparent Mode Alternative ..........D-68 D.8.14 Transparent Mode Summary ..............D-68 An Appletalk Node with the MC68302 and MC68195 ......D-69 D.9.1 Overview of the Board ................D-70 D.9.2 Important Side Notes ................D-70...

- Page 15 PAREC—Receive Parity Error Counter..........E-24 E.2.1.3.6 FRMEC—Receive Framing Error Counter..........E-24 E.2.1.3.7 NOSEC—Receive Noise Counter............E-24 E.2.1.3.8 BRKEC—Receive Break Condition Counter......... E-24 E.2.1.3.9 UADDR1 and UADDR2................. E-24 E.2.1.4 Receive Buffer Descriptors..............E-25 E.2.1.4.1 Receive BD Control/Status Word............E-26 MOTOROLA MC68302 USER’S MANUAL...

- Page 16 Programming the SCC for Transparent ..........E-40 E.3.2.1 CP Initialization ..................E-40 E.3.2.2 General and Transparent Protocol-Specific RAM Initialization ..... E-41 E.3.2.3 SCC Initialization................... E-41 E.3.2.4 SCC Operation..................E-41 E.3.2.5 SCC Interrupt Handling................. E-41 Appendix F Design Checklist MC68302 USER’S MANUAL MOTOROLA...

- Page 17 Figure 2-3. M68000 Bus/Address Error Exception Stack Frame........ 2-10 Figure 2-4. M68000 Short-Form Exception Stack Frame ........... 2-10 Figure 2-5. MC68302 IMP Configuration Control ............2-12 Section 3 System Integration Block (SIB) Figure 3-1. IDMA Controller Block Diagram ..............3-3 Figure 3-2.

- Page 18 Figure 4-42. Transparent Receive Buffer Descriptor..........4-130 Figure 4-43. Transparent Transmit Buffer Descriptor..........4-131 Figure 4-44. SCP Timing .................... 4-135 Figure 4-45. SCP vs. SCC Pin Multiplexing ............... 4-137 Section 5 Signal Description Figure 5-1. Functional Signal Groups................5-3 xviii MC68302 USER’S MANUAL MOTOROLA...

- Page 19 Figure 6-20. IDL Timing Diagram ................. 6-31 Figure 6-21. GCI Timing Diagram................. 6-33 Figure 6-22. PCM Timing Diagram (SYNC Envelopes Data) ........6-35 Figure 6-23. PCM Timing Diagram (SYNC Prior to 8-Bit Data) ........6-35 Figure 6-24. NMSI Timing Diagram ................6-37 MOTOROLA MC68302 USER’S MANUAL...

- Page 20 Figure C-1. CP Architecture Running RAM Microcode ..........C-1 Appendix D MC68302 Applications Figure D-1. MC68302 Minimum System Configuration (Sheet 1 of 2)......D-2 Figure D-2. MC68302 Minimum System Configuration (Sheet 2 of 2)......D-3 Figure D-3. Transmit and Receive BD Structure............D-7 Figure D-4.

- Page 21 Table 4-6. SCC Parameter RAM Memory Map............4-35 Table 4-7. UART Specific Parameter RAM..............4-46 Table 4-8. HDLC-Specific Parameter RAM..............4-69 Table 4-9. BISYNC Specific Parameter RAM ..............4-86 Table 4-10. DDCMP Specific Parameter RAM ............4-104 Table 4-11. Transparent-Specific Parameter RAM ............4-125 MOTOROLA MC68302 USER’S MANUAL...

-

Page 22: Table Title Page

Descriptors for SCCx ................E-31 Table E-3 (b). Transparent Programming Model (Continued) General Parameter and Transparent Protocol-Specific RAM for SCCx ......E-31 Table E-3 (c). SCCx Register Set ................E-32 Table E-3 (d). General Registers (Only One Set) ............E-32 xxii MC68302 USER’S MANUAL MOTOROLA... -

Page 23: General Description

SECTION 1 GENERAL DESCRIPTION The MC68302 integrated multiprotocol processor (IMP) is a very large-scale integration (VL- SI) device incorporating the main building blocks needed for the design of a wide variety of controllers. The device is especially suitable to applications in the communications industry. -

Page 24: General Description

PARALLEL I/O REFRESH CONTROLLER SYSTEM INTEGRATION BLOCK PERIPHERAL BUS 6 CHANNELS SDMA SMC (2) SCC1 SCC2 SCC3 MAIN CONTROLLER (RISC) SERIAL CHANNELS PHYSICAL INTERFACE COMMUNICATIONS PROCESSOR I/O PORTS AND PIN ASSIGNMENTS Figure 1-1. MC68302 Block Diagram MC68302 USER’S MANUAL MOTOROLA... -

Page 25: Features

General Description The MC68302 can also be used in applications such as board-level industrial controllers performing real-time control applications with a local control bus and an X.25 packet network connection. Such a system provides the real-time response to a demanding peripheral while permitting remote monitoring and communication through an X.25 packet network. -

Page 26: Mc68302 System Architecture

CHANNELS Figure 1-2. General-Purpose Microprocessor System Design The MC68302 microprocessor architecture is shown in Figure 1-3. In this architecture, the peripheral devices are isolated from the system bus through a dual-port memory. Various parameters and counters and all memory buffer descriptor tables reside in the dual-port RAM. -

Page 27: Nmsi Communications-Oriented Environment

The net effect is the loss of a single memory access by the CP main controller per M68000 core access. The buffer memory structure of the MC68302 can be configured to closely match I/O chan- nel requirements by careful selection of buffer size and buffer linking. The interrupt structure... -

Page 28: Basic Rate Isdn Or Digital Voice/Data Terminal

A basic rate ISDN (2B + D) or digital voice/data terminal can be made from a chip set based on the MC68302. Refer to Figure 1-5 for an example of a basic rate ISDN voice/data termi- nal. In this terminal, the CP can directly support the 2B + D channels and perform either V.110 or V.120 rate adaption. -

Page 29: Figure 1-4. Nmsi Communications-Oriented Board Design

General Description Figure 1-4. NMSI Communications-Oriented Board Design MOTOROLA MC68302 USER’S MANUAL... -

Page 30: Figure 1-5. Basic Rate Idl Voice/Data Terminal In Isdn

General Description Figure 1-5. Basic Rate IDL Voice/Data Terminal in ISDN MC68302 USER’S MANUAL MOTOROLA... -

Page 31: Mc68000/Mc68008 Core

Integrated Services Digital Network (ISDN). The MC68302 can operate either in the full MC68000 mode with a 16-bit data bus or in the MC68008 mode with an 8-bit data bus by tying the bus width (BUSW) pin low. UDS/A0 func- tions as A0 and LDS/DS functions as DS in the MC68008 mode. -

Page 32: Mc68000/Mc68008 Core

(eight levels available) as well as the following condition codes: overflow (V), zero (Z), negative (N), carry (C), and extend (X). Additional status bits indicate that the processor is in trace (T) mode and/or in a supervisor (S) state. MC68302 USER’S MANUAL MOTOROLA... -

Page 33: Instruction Set Summary

Figure 2-2. M68000 Status Register 2.2 INSTRUCTION SET SUMMARY The five data types supported by the M68000 on the MC68302 are bits, binary-coded deci- mal (BCD) digits (4 bits), bytes (8 bits), words (16 bits), and long words (32 bits). -

Page 34: Table 2-1. M68000 Data Addressing Modes

1 for byte, 2 for word, and 4 for long word. If An is the stack pointer and the operand size is byte, N = 2 to keep the stack pointer on a word boundary. Replaces MC68302 USER’S MANUAL MOTOROLA... -

Page 35: Table 2-2. M68000 Instruction Set Summary

STOP Stop Jump to Subroutine Subtract SWAP Swap Data Register Halves Load Effective Address Test and Set Operand LINK Link Stack TRAP Trap Logical Shift Left TRAPV Trap on Overflow Logical Shift Right Test UNLK Unlink MOTOROLA MC68302 USER’S MANUAL... -

Page 36: Address Spaces

In the M68000 Family, the address spaces are indicated by function code pins. On the M68000, three function code pins are output from the device on every bus cycle of every executed instruction. This provides the purpose of each bus cycle to external logic. MC68302 USER’S MANUAL MOTOROLA... -

Page 37: Table 2-4. M68000 Address Spaces

On the MC68302, this capability is provided for each potential internal bus master (i.e., the IDMA, SDMA, and DRAM refresh units). Also on the MC68302, provision is made for the decoding of function codes that are output from external bus masters (e.g., in the chip-select generation logic). -

Page 38: Exception Processing

Table 2-5. M68000 Exception Vector Assignment Vector Address Decimal Space Assignment Number Reset: Initial SSP Reset: Initial PC Bus Error Address Error Illegal Instruction Zero Divide CHK Instruction TRAPV Instruction Privilege Violation Trace Line 1010 Emulator MC68302 USER’S MANUAL MOTOROLA... -

Page 39: Exception Stacking Order

NOTES: 1. Vector numbers 12–14, 16–23, and 48–63 are reserved for future enhancements by Motorola (with vectors 60–63 being used by the M68302 (see 2.7 MC68302 IMP Configuration and Control)). No user peripheral devices should be assigned these numbers. 2. Unlike the other vectors which only require two words, reset vector (0) requires four words and is located in the supervisor program space. -

Page 40: Figure 2-3. M68000 Bus/Address Error Exception Stack Frame

PROGRAM COUNTER HIGH PROGRAM COUNTER LOW Figure 2-4. M68000 Short-Form Exception Stack Frame NOTE The MC68302 uses the exact same exception stack frames as the MC68000. For exception processing times and instruction execution times, refer to MC68000UM/AD, 8-/16-/32-Bit Microprocessor User's Manual . -

Page 41: Interrupt Processing

MC68000-core-initiated read-modify-write cycle. The MC68302 can be programmed to use the RMC signal to negate address strobe (AS) at the end of the read portion of the cycle and assert AS at the beginning of the write portion of the cycle (See 3.8.3 System Control Bits). -

Page 42: Mc68302 Imp Configuration Control

3.8.1 System Control Register (SCR). The CKCR entry contains the CKCR reg- ister described in 3.9 Clock Control Register. Figure 2-5 shows all the MC68302 IMP on-chip addressable locations and how they are mapped into system memory. SYSTEM MEMORY MAP... - Page 43 4K-byte block of on-chip peripherals. The address compare logic uses these bits, dependent upon the CFC bit, to cause an address match within its address space. NOTE Do not assign this field to the M68000 core interrupt acknowl- edge space (FC2–FC0 = 7). MOTOROLA MC68302 USER’S MANUAL 2-13...

-

Page 44: Mc68302 Memory Map

The following tables show the additional registers added to the M68000 to make up the MC68302. All of the registers are memory-mapped. Four entries in the M68000 exception vectors table (located in low RAM) are reserved for addresses of system configuration reg- isters (see Table 2-6) that reside on-chip. -

Page 45: Table 2-8. Parameter Ram

4.5 Serial Communication Controllers (SCCs). Base + 67E contains the MC68302 revi- sion number. Revision A parts (mask 1B14M) correspond to the value $0001. Revision B parts (mask 2B14M and 3B14M which are described in this manual) correspond to the value $0002. - Page 46 SMC1–SMC2 Internal Use Base +67A Word Rx/TxBD SCC1–SCC3 BERR Channel Number Base +67C Word Base +67E # Word MC68302 Revision Number Base + 680 SCC3 • • Specific Protocol Parameters • Base + 6BF SCC3 Base + 6C0 • Reserved •...

-

Page 47: Table 2-9. Internal Registers

Option Register 1 DFFD Base + 838 # Base Register 2 C000 Base + 83A # Option Register 2 DFFD Base + 83C # Base Register 3 C000 Option Register 3 DFFD Base + 83E # MOTOROLA MC68302 USER’S MANUAL 2-17... - Page 48 Base + 899 SCC2 Reserved Base + 89A SCCM2 SCC2 SCC2 Mask Register Base + 89B SCC2 Reserved Base + 89C SCCS2 SCC2 SCC2 Status Register Base + 89D SCC2 Reserved Base + 89E SCC2 2-18 MC68302 USER’S MANUAL MOTOROLA...

-

Page 49: Event Registers

(RST) bit located in a register in that block. This RST bit will reset that entire block, including any event registers contained therein. Examples: 1. To clear bit 0 of SCCE1, execute "MOVE.B #$01,SCCE1" MOTOROLA MC68302 USER’S MANUAL 2-19... - Page 50 Thus, if a bit is a one when read, it will be written back with a one, clearing that bit. For example, the in- struction “BSET.B #0,SCCE1” will actually clear ALL bits in SCCE1, not just bit 0. 2-20 MC68302 USER’S MANUAL MOTOROLA...

-

Page 51: System Integration Block (Sib)

SECTION 3 SYSTEM INTEGRATION BLOCK (SIB) The MC68302 contains an extensive SIB that simplifies the job of both the hardware and software designer. It integrates the M68000 core with the most common peripherals used in an M68000-based system. The independent direct memory access (IDMA) controller re- lieves the hardware designer of the extra effort and board logic needed to connect an exter- nal DMA controller. -

Page 52: Dma Control

Note that the chip se- lect and wait state generation logic on the MC68302 may be used with the IDMA, if desired. Every IDMA cycle requires between two and four bus cycles, depending on the address boundary and transfer size. -

Page 53: Idma Registers (Independent Dma Controller)

Figure 3-1. IDMA Controller Block Diagram 3.1.2 IDMA Registers (Independent DMA Controller) The IDMA has six registers that define its specific operation. These registers include a 32- bit source address pointer register (SAPR), a 32-bit destination address pointer register MOTOROLA MC68302 USER’S MANUAL... -

Page 54: Channel Mode Register (Cmr)

1 = If a bus error occurs during an operand transfer either on BES or BED, the channel generates an interrupt to the IMP interrupt controller and sets the appropriate bit (BES or BED) in the CSR. MC68302 USER’S MANUAL MOTOROLA... - Page 55 00 = IDMA gets up to 75% of the bus bandwidth. 01 = IDMA gets up to 50% of the bus bandwidth. 10 = IDMA gets up to 25% of the bus bandwidth. 11 = IDMA gets up to 12.5% of the bus bandwidth. MOTOROLA MC68302 USER’S MANUAL...

-

Page 56: Source Address Pointer Register (Sapr)

$00000000. This register can be incremented by one or two, depending on the SSIZE bit and the starting address in this register. 3.1.2.3 Destination Address Pointer Register (DAPR) The DAPR is a 32-bit register. RESERVED DESTINATION ADDRESS POINTER MC68302 USER’S MANUAL MOTOROLA... -

Page 57: Function Code Register (Fcr)

A bit is cleared by writing a one and is left unchanged by writing a zero. More than one bit may be cleared at a time, and the register is cleared at reset. RESERVED DONE Bits 7–4—These bits are reserved for future use. MOTOROLA MC68302 USER’S MANUAL... -

Page 58: Interface Signals

DONE may be used as an input to the IDMA controller indicating that the device being serviced requires no more transfers and that the transmission is to be ter- minated. DONE is an output if the transfer count is exhausted. MC68302 USER’S MANUAL MOTOROLA... -

Page 59: Idma Operational Description

When the complete operand is written, the DAPR is incremented by one or two, and the BCR is decremented by the number of bytes transferred. See 3.1.2.3 Desti- nation Address Pointer Register (DAPR) and 3.1.2.5 Byte Count Register (BCR) for more details. MOTOROLA MC68302 USER’S MANUAL... -

Page 60: Address Sequencing

16 Bit Byte Word Operand Packing Read Word—Write Byte, Write Byte 16 Bit Word Byte Operand Unpacking 16 Bit Word Word Read Word—Write Word Refer toTable 3-2 for more details on the IDMA bus cycles. 3-10 MC68302 USER’S MANUAL MOTOROLA... -

Page 61: Transfer Request Generation

External Burst Mode For external devices requiring very high data transfer rates, the external burst mode al- lows the IDMA to use all the bus bandwidth to service the device. In the burst mode, the MOTOROLA MC68302 USER’S MANUAL 3-11... -

Page 62: Block Transfer Termination

STR is cleared, and an interrupt is generated if INTN is set. The SAPR and/or DAPR are also incremented in the normal fashion. NOTE If the channel is started with BCR value set to zero, the channel will transfer 64K bytes. 3-12 MC68302 USER’S MANUAL MOTOROLA... -

Page 63: Idma Programming

IDMA status changes, status bits are set in the CSR but not in the IPR. When either INTN or INTE is set and the corresponding event occurs, the appropriate bit is set in the IPR, and, if this bit is not masked, the interrupt controller will interrupt the M68000 core. MOTOROLA MC68302 USER’S MANUAL 3-13... -

Page 64: Dma Bus Arbitration

M68000 core: reset, bus error, halt, and retry. NOTE These exceptions also apply to the SDMA channels except that the bus error reporting method is different. See 4.5.8.4 Bus Error on SDMA Access for further details. 3-14 MC68302 USER’S MANUAL MOTOROLA... -

Page 65: Reset

• Two Operational Modes: Normal and Dedicated • Eighteen Prioritized Interrupt Sources (Internal and External) • A Fully Nested Interrupt Environment • Unique Vector Number for Each Internal/External Source Generated • Three Interrupt Request and Interrupt Acknowledge Pairs MOTOROLA MC68302 USER’S MANUAL 3-15... -

Page 66: Overview

1. The interrupt controller on the IMP collects interrupt events from on and off-chip pe- ripherals, prioritizes them, and presents the highest priority request to the M68000 core. 2. The M68000 responds to the interrupt request by executing an interrupt acknowledge 3-16 MC68302 USER’S MANUAL MOTOROLA... -

Page 67: Interrupt Controller Overview

In this mode, the three external interrupt request pins are configured as IPL2–IPL0 as in the original MC68000. Up to seven levels of interrupt priority may be encoded. Level 4 is reserved for IMP INRQ interrupts and may not be generated by an external device. MOTOROLA MC68302 USER’S MANUAL 3-17... -

Page 68: Interrupt Priorities

INRQ interrupts are assigned to level 4 (fixed). EXRQ interrupts are assigned by the user to any of the remaining six priority levels in normal mode. In dedi- cated mode, EXRQ interrupts may be assigned to priority levels 7, 6, and 1. 3-18 MC68302 USER’S MANUAL MOTOROLA... -

Page 69: Inrq Interrupt Source Priorities

M68000 core for servicing. After the vector number corresponding to this interrupt is passed to the core during an interrupt acknowledge cycle, an INRQ interrupt request is cleared in IPR. (EXRQ requests must be cleared externally.) The remaining interrupt MOTOROLA MC68302 USER’S MANUAL 3-19... -

Page 70: Masking Interrupt Sources And Events

By clearing all unmasked bits in the event register, the IPR bit is also cleared. 3-20 MC68302 USER’S MANUAL MOTOROLA... -

Page 71: Interrupt Vector

The IMP can generate vectors for up to seven external peripherals by connecting the exter- nal request lines to IRQ7, IRQ6, IRQ1, PB11, PB10, PB9, and PB8. PB11, PB10, PB9, and PB8 are prioritized within level 4. MOTOROLA MC68302 USER’S MANUAL 3-21... - Page 72 3-4. When the core initiates an interrupt acknowledge cycle for level 4 and there is no internal interrupt pending, the interrupt controller encodes the error code 00000 onto the five low-order bits of the interrupt vector. 3-22 MC68302 USER’S MANUAL MOTOROLA...

-

Page 73: Figure 3-4. Scc1 Vector Calculation Example

PURPOSELY CHOSEN TO CAUSE THIS. 3. READ 32-BIT VALUE AT $2B4 AND JUMP INTERRUPT HANDLER BEGINS AT $2B4 0007 $070302 (24-BIT ADDRESSES ARE USED $2B6 0302 ON THE M68000). Figure 3-4. SCC1 Vector Calculation Example MOTOROLA MC68302 USER’S MANUAL 3-23... -

Page 74: Interrupt Controller Programming Model

0 = Internal vector. The interrupt controller will provide the vector number for a level 1 interrupt acknowledge cycle. 1 = External vector. The interrupt controller will not provide the vector number for a lev- el 1 interrupt. 3-24 MC68302 USER’S MANUAL MOTOROLA... - Page 75 IOUT2–IOUT0 to another pro- cessor (MC68302, MC68020, etc.) For cases when the slave MC68302 does not generate a level 4 vector (i.e., the VGE bit is cleared), one must set the ET1, ET6, and ET7 bits to level-trig- gered and then negate the IRQ1, IRQ6, and IRQ7 lines external- ly in the interrupt handler code.

-

Page 76: Interrupt Pending Register (Ipr)

The ERR bit is set if the user drives the IPL2–IPL0 lines to inter- rupt level 4 and no INRQ interrupt is pending. PB11 PB10 SCC1 SDMA IDMA SCC2 TIMER1 SCC3 TIMER2 TIMER3 SMC1 SMC2 3-26 MC68302 USER’S MANUAL MOTOROLA... -

Page 77: Interrupt Mask Register (Imr)

To clear bits that were set by multiple interrupt events, the user should clear all the unmasked events in the corresponding on- chip peripheral's event register. PB11 PB10 SCC1 SDMA IDMA SCC2 TIMER1 SCC3 TIMER2 TIMER3 SMC1 SMC2 — MOTOROLA MC68302 USER’S MANUAL 3-27... -

Page 78: Interrupt In-Service Register (Isr)

Example 1—Timer 3 (Software Watchdog Timer) Interrupt Handler 1. Vector to interrupt handler. 2. (Handle Event) 3. Clear the TIMER3 bit in the ISR. 4. Execute RTE instruction. Example 2— SCC1 Interrupt Handler 1. Vector to interrupt handler. 3-28 MC68302 USER’S MANUAL MOTOROLA... -

Page 79: Parallel I/O Ports

A control register (PACNT) bit is cleared. Port A pins are configured as dedicated on-chip peripheral pins if the corresponding PACNT bit is set. An example block diagram of PA0 is given in Figure 3-5 MOTOROLA MC68302 USER’S MANUAL 3-29... -

Page 80: Figure 3-5. Parallel I/O Block Diagram For Pa0

SCC2 to operate in a nonmultiplexed mode without the modem control lines and exter- nal clocks (RCLK2, TCLK2, CD2, CTS2, and RTS2) may dedicate the data lines (RXD2 and TXD2) to SCC2 and configure the others as general-purpose I/O pins. What the peripheral 3-30 MC68302 USER’S MANUAL MOTOROLA... -

Page 81: Port B

PB7–PB0 functions exactly like PA15–PA0, except that PB7–PB0 is controlled by the port B control register (PBCNT), the port B data direction register (PBDDR), and the port B data register (PBDAT), and PB7 is configured as an open-drain output (WDOG) upon total system reset. MOTOROLA MC68302 USER’S MANUAL 3-31... -

Page 82: Pb11-Pb8

The I/O port consists of three memory-mapped read-write 16-bit registers for port A and three memory-mapped read-write 16-bit registers for port B. Refer to Figure 3-6 for the I/O port registers. The reserved bits are read as zeros. 3-32 MC68302 USER’S MANUAL MOTOROLA... -

Page 83: Dual-Port Ram

The CP has 1152 bytes of static RAM configured as a dual-port memory. The dual-port RAM can be accessed by the CP main controller or by one of three bus masters: the M68000 core, the IDMA, or an external master. The M68000 core and the IDMA access the RAM synchro- MOTOROLA MC68302 USER’S MANUAL 3-33... - Page 84 As CP microcode RAM, it is used exclusively to store microcode for the CP main con- troller, allowing the development of special protocols or protocol enhancements, under spe- cial arrangement with Motorola. Appendix C discusses available offerings. The RAM block diagram is shown in Figure 3-7. The M68000 core, the IDMA, and the ex- ternal master access the RAM through the IMP bus interface unit (BIU) using the M68000 bus.

-

Page 85: Timers

ADDRESS Figure 3-7. RAM Block Diagram 3.5 TIMERS The MC68302 includes three timer units: two identical general-purpose timers and a soft- ware watchdog timer. Each general-purpose timer consists of a timer mode register (TMR), a timer capture regis- ter (TCR), a timer counter (TCN), a timer reference register (TRR), and a timer event register (TER). -

Page 86: Timer Key Features

• Programmable Sources for the Clock Input • Input Capture Capability • Output Compare with Programmable Mode for the Output Pin • Two Timers Cascadable to Form a 32-Bit Timer • Free Run and Restart Modes 3-36 MC68302 USER’S MANUAL MOTOROLA... -

Page 87: General Purpose Timer Units

The timer registers may be modified at any time by the user. 3.5.2.1 Timer Mode Register (TMR1, TMR2) TMR1 and TMR2 are identical 16-bit registers. TMR1 and TMR2, which are memory- mapped read-write registers to the user, are cleared by reset. PRESCALER VALUE (PS) ICLK MOTOROLA MC68302 USER’S MANUAL 3-37... -

Page 88: Timer Reference Registers (Trr1, Trr2)

(see 3.5.2.6 General Purpose Timer Example). 3.5.2.2 Timer Reference Registers (TRR1, TRR2) Each TRR is a 16-bit register containing the reference value for the timeout. TRR1 and TRR2 are memory-mapped read-write registers. 3-38 MC68302 USER’S MANUAL MOTOROLA... -

Page 89: Timer Capture Registers (Tcr1, Tcr2)

INRQ to the interrupt controller. This register is cleared at reset. RESERVED CAP—Capture Event The counter value has been latched into the TCR. The CE bits in the TMR are used to enable the interrupt request caused by this event. MOTOROLA MC68302 USER’S MANUAL 3-39... -

Page 90: General Purpose Timer Example

1. Program the Port B control register to change the port pin from a general purpose input pin to TOUT. 2. Program the TRR to $61A8 ( = 50000/2). 3. Program the TMR to $321B (prescaler = 3, OM =1 to toggle TOUT, FRR = 1 to restart 3-40 MC68302 USER’S MANUAL MOTOROLA... -

Page 91: Timer 3 - Software Watchdog Timer

Reset initializes the register to $FFFF, enabling the watchdog timer and setting it to the max- imum timeout period. This causes a timeout to occur if there is an error in the boot program. MOTOROLA MC68302 USER’S MANUAL 3-41... -

Page 92: Software Watchdog Counter (Wcn)

3.6 EXTERNAL CHIP-SELECT SIGNALS AND WAIT-STATE LOGIC The MC68302 provides a set of four programmable chip-select signals. Each chip-select signal has an identical internal structure. For each memory area, the user may also define an internally generated cycle termination signal (DTACK). - Page 93 A priority structure exists within the chip-select block. For a given address, the priority is as follows: 1. Access to any IMP internal address (BAR, dual-port RAM, etc.) No chip select asserted. 2. Chip Select 0 3. Chip Select 1 4. Chip Select 2 5. Chip Select 3 MOTOROLA MC68302 USER’S MANUAL 3-43...

-

Page 94: Figure 3-9. Chip-Select Block Diagram

(WPVE) is set. The CS line will not be asserted. NOTE The chip-select logic is reset only on total system reset (asser- tion of RESET and HALT). Accesses to the internal RAM and registers, including the system configuration registers (BAR and 3-44 MC68302 USER’S MANUAL MOTOROLA... -

Page 95: Chip-Select Logic Key Features

FC2–FC0 —Function Code Field This field is contained in bits 15–13 of each BR. These bits are used to set the address space function code. The address compare logic uses these bits to determine whether an MOTOROLA MC68302 USER’S MANUAL 3-45... - Page 96 On write protect violation cycles (RW = 0 and MRW = 1), BERR will be generated if WPVE is set, and WPV will be set. If the write protect mechanism is used by an external master, the R/W low to AS asserted timing should be 16 ns minimum. 3-46 MC68302 USER’S MANUAL MOTOROLA...

-

Page 97: Option Registers (Or3-Or0)

The CS lines are asserted slightly earlier for internal IMP master memory cycles than for an external master using the CS lines. Set external master wait state (EMWS) in the SCR whenever these timing differences require an extra memory wait state for external masters. MOTOROLA MC68302 USER’S MANUAL 3-47... -

Page 98: Chip Select Example

Set up chip select 2 to assert for a 1 Megabyte block of external RAM beginning at $200000 with 1 wait state. Note that the address must be on a block boundary (i.e. the starting ad- dress of a 1 Megabyte block could not be $210000). 3-48 MC68302 USER’S MANUAL MOTOROLA... -

Page 99: On-Chip Clock Generator

(C L ) of this circuit is 20 pF, calculated as (C1 + C in )/2, where C1 = C2 = 25 pF and C in = 15 pF maximum on the EXTAL pin. MC68302 EXTAL XTAL Figure 3-10. Using an External Crystal MOTOROLA MC68302 USER’S MANUAL 3-49... -

Page 100: System Control

The SCR is a memory-mapped read-write register. The address of this register is fixed at $0F4 in supervisor data space (FC = 5). ERRE WPVE RMCST EMWS ADCE BCLM FRZW FRZ2 FRZ1 HWDEN HWDCN2–HWDCN0 LPREC LPP16 LPEN LOW-POWER CLOCK DIVIDER Figure 3-11. System Control Register 3-50 MC68302 USER’S MANUAL MOTOROLA... -

Page 101: System Status Bits

In the case of nested interrupts, the user may wish to clear the IPA bit only at the end of the original lower priority interrupt rou- tine to keep BCLR asserted until it completes. To guarantee that MOTOROLA MC68302 USER’S MANUAL 3-51... -

Page 102: System Control Bits

WPVE—Write Protect Violation Enable 0 = BERR is not asserted when a write protect violation occurs. 1 = BERR is asserted when a write protect violation occurs. After system reset, this bit defaults to zero. 3-52 MC68302 USER’S MANUAL MOTOROLA... - Page 103 1 = The MC68302 uses RMC to negate AS and CS at the end of the read portion of the RMC cycle and reasserts AS and CS at the beginning of the write portion. BG will not be asserted until the end of the write portion.

-

Page 104: Disable Cpu Logic (M68000)

MC68302. In applications such as disable CPU mode, in which the M68000 core is not operating, the user should note that SAM may be changed by an external master on the first access of the MC68302, but that first write access must be asynchronous with three wait states. - Page 105 2. BG will be an input to the IDMA and SDMA from the external M68000 bus, rather than being an output from the MC68302. When BG is sampled as low by the MC68302, it waits for AS, BERR, HALT, and BGACK to be negated, and then asserts BGACK and performs one or more bus cycles.

-

Page 106: Bus Arbitration Logic

IDMA channels do not affect BR and BG, but only BGACK (unless disable CPU mode is used). The MC68302 provides several options for changing the preceding bus master priority list. The options are configured by setting the BCLM bit in the SCR and deciding whether or not the BCLR pin is used externally to cause external bus masters to relinquish the bus (see Table 3-10). -

Page 107: Figure 3-12. Imp Bus Arbiter

ER + CG IR & CG EXTERNAL BUS REQUEST INTERNAL BUS REQUEST (IDMA OR SDMA) CORE BUS GRANT EXTERNAL GRANT INTERNAL GRANT ER & CG IDLE BUS IDLE OR CORE CYCLE Figure 3-12. IMP Bus Arbiter MOTOROLA MC68302 USER’S MANUAL 3-57... -

Page 108: External Bus Arbitration

An external bus master may gain ownership of the M68000 bus by asserting the bus request (BR) pin. After gaining ownership, it may access the IMP registers or RAM or any system memory address. Chip selects and system control functions, such as the hardware watch- dog, continue to operate. 3-58 MC68302 USER’S MANUAL MOTOROLA... -

Page 109: Hardware Watchdog

The hardware watchdog logic uses four bits in the SCR. HWDEN—Hardware Watchdog Enable 0 = The hardware watchdog is disabled. 1 = The hardware watchdog is enabled. After system reset, this bit defaults to one to enable the hardware watchdog. MOTOROLA MC68302 USER’S MANUAL 3-59... -

Page 110: Reducing Power Consumption

M68000 core and when it is desirable to reduce system power consumption to its minimum value. All low-power modes are entered by first setting the low-power enable (LPEN) bit, and then executing the M68000 STOP in- struction. 3-60 MC68302 USER’S MANUAL MOTOROLA... -

Page 111: Low-Power Mode

5. When a timer 1 or 2 interrupt occurs, the M68000 resumes execution with the timer 1 or 2 interrupt handler. After the RTE instruction, execution continues with the instruc- tion following the STOP instruction in step 4 above. All IMP state information is re- tained. MOTOROLA MC68302 USER’S MANUAL 3-61... -

Page 112: Lowest Power Mode

NOTE The use of external clocks with the SCCs allows the original se- rial rates to be maintained; however, before attempting this, the SCC performance data should be carefully reviewed (see Ap- 3-62 MC68302 USER’S MANUAL MOTOROLA... - Page 113 LPCD0 0 to 31) can be selected. After a system reset, these bits default to zero. LPEN—Low-power Enable 0 = The low-power modes are disabled. 1 = The low-power modes are enabled. After a system reset, this bit defaults to zero to disable the low-power modes. MOTOROLA MC68302 USER’S MANUAL 3-63...

-

Page 114: Clock Control Register

TCLK1. This option may also be chosen if it is re- quired to run the SCC1 baud rate generator at high speed (for instance in a high speed UART application), but the TCLK1 output is not needed, and it is desired to 3-64 MC68302 USER’S MANUAL MOTOROLA... -

Page 115: Freeze Control

Although DBRG1 may be modified at any time, the user should note that glitches on BRG1 are not prevented by the MC68302 when the state of DBRG1 is changed. Bits 10 - 0—Reserved. Should be written with zeros. -

Page 116: Dynamic Ram Refresh Controller

RAM (DRAM) refresh task without any intervention from the M68000 core. Use of this feature requires a timer or SCC baud rate generator (either from the MC68302 or ex- ternally), the I/O pin PB8, and two transmit buffer descriptors from SCC2 (Tx BD6 and Tx BD7). -

Page 117: Dram Refresh Controller Bus Timing

The refresh operation is a byte read operation. Thus, UDS or LDS will be asserted from the MC68302, but not both. A refresh to an odd address will assert LDS; whereas, a refresh to an even address will assert UDS. -

Page 118: Initialization

RAM starting address. This param- eter should be initialized by the user before activating the refresh routine. NOTE The FC bits should not be programmed to the value “111.” 3-68 MC68302 USER’S MANUAL MOTOROLA... -

Page 119: Programming Example

IMP. Depending on the PAL design, an increment value of $0002 can actually refresh a word at a time, even though the refresh access from the MC68302 is a byte read. The COUNT value is the number of word refreshes required in the entire DRAM bank. - Page 120 System Integration Block (SIB) 3-70 MC68302 USER’S MANUAL MOTOROLA...

-

Page 121: Communications Processor (Cp)

• Six Serial Direct Memory Access (SDMA) Channels • A Command Set Register • Serial Channels Physical Interface Including: —Motorola Interchip Digital Link (IDL) —General Circuit Interface (GCI), also known as IOM-2 —Pulse Code Modulation (PCM) Highway Interface —Nonmultiplexed Serial Interface (NMSI) Implementing Standard —Modem Signals... -

Page 122: Figure 4-1. Simplified Cp Architecture

The main controller has a priority scheduler that determines which microcode routine is called when more than one internal request is pending. Requests are serviced in the follow- ing priority: 1. CP or System Reset 2. SDMA Bus Error MC68302 USER’S MANUAL MOTOROLA... -

Page 123: Sdma Channels

RAM as shown in path 1. In path 2, data is sent over the peripheral bus to the in- ternal dual-port RAM. The SMCs and SCP, shown in path 3, always route their data to the dual-port RAM since they only receive and transmit a byte at a time. MOTOROLA MC68302 USER’S MANUAL... -

Page 124: Figure 4-2. Three Serial Data Flow Paths

HDLC or transparent protocols where it writes 16 bits at a time. Each bus cycle is a standard M68000-type bus cycle. The chip select and wait state generation logic on the MC68302 may be used with the SDMA channels. NOTE... -

Page 125: Command Set

For instance, BCLR can be connected through logic to the external master's HALT signal, and then be negated exter- nally when the external master's AS signal is negated. BCLR as seen from the MC68302 is negated by the SDMA during its access to memory. - Page 126 CH. NUM.—Channel Number These bits are set by the M68000 core to define the specific SCC channel that the com- mand is to operate upon. 00 = SCC1 01 = SCC2 10 = SCC3 11 = Reserved MC68302 USER’S MANUAL MOTOROLA...

-

Page 127: Command Execution Latency

3. IDL—Interchip Digital Link 4. GCI—General Circuit Interface The most generic physical interface on the MC68302 is the nonmultiplexed serial interface (NMSI). The NMSI consists of seven of the basic modem (or RS-232) signals: TXD, TCLK, RXD, RCLK, RTS, CTS, and CD. Each SCC can have its own set of NMSI signals as shown in Figure 4-3. -

Page 128: Figure 4-3. Nmsi Physical Interface

I/O. If a multiplexed mode is chosen, the baud rate gen- erator clock is output on the BRG or TCLK pin, depending on whether the NMSI mode or multiplexed mode, respectively, was chosen for that SCC. MC68302 USER’S MANUAL MOTOROLA... -

Page 129: Figure 4-4. Multiplexed Mode On Scc1 Opens Additional Configuration Possibilities

NOTE: MUX is defined as one of the following: IDL, GCI, or PCM highway. The PCM highway interface is a flexible time-division multiplexed interface. It allows the MC68302 to connect to popular time-slot interfaces such as T1 and CEPT as well as user- defined time-slot interfaces. -

Page 130: Figure 4-5. Serial Channels Physical Interface Block Diagram

When using the IDL or GCI buses, additional control functions in the frame structure are re- quired. These functions are supported in the MC68302 through two SMC channels: SMC1 and SMC2. (For other matters relating to the SMCs, refer to 4.7 Serial Management Con- trollers (SMCs)). -

Page 131: Idl Interface

The IDL interface is a full-duplex ISDN interface used to interconnect a physical layer device (such as the Motorola ISDN S/T transceiver MC145474) to the integrated multiprotocol pro- cessor (IMP). Data on five channels (B1, B2, D, A, and M) is transferred in a 20-bit frame every 125 s, providing 160-kbps full-duplex bandwidth. -

Page 132: Figure 4-7. Idl Terminal Adaptor

B1 and B2 channels. These signals are used for interfacing devices that do not support the IDL bus. These signals, configured by the SIMASK register, are active only for bits that are not masked. The IDL signals are as follows: 4-12 MC68302 USER’S MANUAL MOTOROLA... - Page 133 D channel. If a collision is detected on the D channel, the physical layer device ne- gates L1GR. The IMP then stops its transmission and retransmits the frame when L1GR is asserted again. This is handled automatically for the first two buffers of the frame. MOTOROLA MC68302 USER’S MANUAL 4-13...

-

Page 134: Gci Interface

B1 and B2 channels and the data rate clock (L1CLK). These signals are used for interfacing devices that do not support the GCI bus. They are configured with the SIMASK register and are active only for bits that are not masked. 4-14 MC68302 USER’S MANUAL MOTOROLA... -

Page 135: Figure 4-8. Gci Bus Signals

64-kbps Monitor Channel (8 bits) 16-kbps Signaling Channel (2 bits) C/I, A, E 48-kbps Command/Indication Channel (6 bits) In addition to the 144-kbps ISDN 2B + D channels, GCI provides two channels for mainte- nance and control functions. MOTOROLA MC68302 USER’S MANUAL 4-15... -

Page 136: Pcm Highway Mode

In PCM highway mode, one, two, or all three SCCs can be multiplexed together to support various time-division multiplexed interfaces. PCM highway supports the standard T1 and CEPT interfaces as well as user-defined interfaces. In this mode, the NMSI1 pins have new names and functions (see Table 4-2). 4-16 MC68302 USER’S MANUAL MOTOROLA... -

Page 137: Table 4-2. Pcm Highway Mode Pin Functions

Three Request-to-Send Signals Outputs L1CLK is always an input to the MC68302 in PCM highway mode and is used as both a re- ceive and transmit clock. Thus, data is transmitted and received simultaneously in PCM highway mode. (If receive data needs to be clocked into the MC68302 at a different time or speed than transmit data is being clocked out, then NMSI mode should be used instead of PCM highway.) -

Page 138: Figure 4-9. Two Pcm Sync Methods

RTS signals are not needed, they can be ignored or reassigned as parallel I/O. 1 CLOCK CYCLE SYNC PRIOR L1SY0 L1SY1 8-BIT ENVELOPE L1SY0 L1SY1 DATA ROUTING CH-1 CH-2 CH-3 Figure 4-9. Two PCM Sync Methods 4-18 MC68302 USER’S MANUAL MOTOROLA... -

Page 139: Nonmultiplexed Serial Interface (Nmsi)

If the IDL or GCI mode is used, this register allows the user to support any or all of the ISDN channels independently. Any extra SCC channel can then be used for other purposes in MOTOROLA MC68302 USER’S MANUAL 4-19... - Page 140 This mode may be used to accomplish multiplex mode loopback testing without affecting the multiplexed layer 1 interface. It also prevents an SCC's indi- vidual loopback (configured in the SCM) from affecting the pins of its associated NMSI interface. 4-20 MC68302 USER’S MANUAL MOTOROLA...

- Page 141 (RXD1, TXD1, RCLK1, TCLK1, CD1, CTS1, and RTS1). SCC2 functions can be routed to port A as NMSI functions or configured instead as PA6–PA0. Four of the SCC3 functions can be routed to port A or retained as PA11–PA8. The other MOTOROLA MC68302 USER’S MANUAL 4-21...

-

Page 142: Serial Interface Mask Register (Simask)

This configuration provides the user with options for controlling up to three independent full-duplex lines implementing bridges or gateway functions or multiplexing up to three SCCs onto the same physical layer interface to implement a 2B + D ISDN basic rate channel or 4-22 MC68302 USER’S MANUAL MOTOROLA... - Page 143 B pins as inputs in the port B data direction register. When a change in the state of the pin occurs, the interrupt handler may assert or negate the extra outputs to sup- port the hand-shaking protocol. (See 3.3 Parallel I/O Ports for related details.) MOTOROLA MC68302 USER’S MANUAL 4-23...

-

Page 144: Scc Features

4.5.2 SCC Configuration Register (SCON) Each SCC controller has a configuration register that controls its operation and selects its clock source and baud rate. Figure 4-12 shows one of the three SCC baud rate generators. 4-24 MC68302 USER’S MANUAL MOTOROLA... - Page 145 RCLK pin. This bit should be programmed to one if a multiplexed mode is chosen for the SCC. After system reset, SCC hardware causes the RCLK to default to an input and stay an input until a zero is written to RCS. MOTOROLA MC68302 USER’S MANUAL 4-25...

-

Page 146: Asynchronous Baud Rate Generator Examples

3 (programmed as 2 in the SCON) and a 16.67-MHz crystal gives a UART clock rate of 5.56 MHz and a baud rate of 347 kbaud. Assuming again a 16.67-MHz 4-26 MC68302 USER’S MANUAL MOTOROLA... -

Page 147: Synchronous Baud Rate Generator Examples

00 = Normal operation (CTS, CD lines under automatic control) In this mode, the CTS and CD lines are monitored by the SCC controller. The SCC controller uses these lines to automatically enable/disable reception and transmission. MOTOROLA MC68302 USER’S MANUAL 4-27... -

Page 148: Table 4-5. Transmit Data Delay (Tclk Periods)

The value on the RXD pin is ignored. For the NMSI2 and NMSI3 pins, the TXD pin may be programmed to either show the transmitted data or not show the data by programming port A par- 4-28 MC68302 USER’S MANUAL MOTOROLA... -

Page 149: Figure 4-13. Output Delays From Rts Low, Synchronous Protocol

SDIAG1–SDIAG0 bits need be set. When using loopback mode, the clock source for the transmitter and the receiver (as set in the TCS and RCS bits in the SCON register), must be the same. Thus, MOTOROLA MC68302 USER’S MANUAL 4-29... - Page 150 The other two combinations are not allowed in this mode. NOTE If external loopback is desired (i.e., external to the MC68302), then the DIAG1–DIAG0 bits should be set for either normal or software operation, and an external connection should be made between the TXD and RXD pins.

-

Page 151: Scc Data Synchronization Register (Dsr)

Note that for the DDCMP, SYN1 must equal SYN2 must equal DSYN1 for proper operation. SYN2 SYN1 NOTE The DSR register has no relationship to the RS-232 signal “data set ready,” which is also abbreviated DSR. MOTOROLA MC68302 USER’S MANUAL 4-31... -

Page 152: Buffer Descriptors Table

SCC1 BUFFER DESCRIPTORS FRAME STATUS TABLE DATA COUNT SCC2 BUFFER DESCRIPTORS DATA POINTER RX DATA BUFFER TABLE SCC3 BUFFER DESCRIPTORS DATA TABLE SCP DESCRIPTOR SMC1 DESCRIPTOR TX DATA SMC2 DESCRIPTOR RX DATA Figure 4-15. Memory Structure 4-32 MC68302 USER’S MANUAL MOTOROLA... -

Page 153: Figure 4-16. Scc Buffer Descriptor Format

Thus, the CP does no look-ahead BD processing, nor does it skip over BDs that are not ready. When the CP sees the “wrap” bit set in a BD, it goes back to the beginning of the BD MOTOROLA MC68302 USER’S MANUAL 4-33... -

Page 154: Scc Parameter Ram Memory Map

RAM areas. Part of each SCC parameter RAM (offset $80–$9A), which is iden- tical for each protocol chosen, is shown in Table 4-6. Offsets $9C–$BF comprise the proto- col-specific portion of the SCC parameter RAM and are discussed relative to the particular protocol chosen. 4-34 MC68302 USER’S MANUAL MOTOROLA... -

Page 155: Data Buffer Function Code Register (Tfcr, Rfcr)

The value of the function code register for any channel may be equal to that of any other, but do not initialize FC2–FC0 with the value “111” which causes a conflict with the interrupt acknowl- edge cycle to occur. MOTOROLA MC68302 USER’S MANUAL 4-35... -

Page 156: Maximum Receive Buffer Length Register (Mrblr)

Tx BD 1, TBD# = $48, etc. Upon reset, the CP main controller sets this register to $40. The user can change this register only after the STOP TRANSMIT command has been issued. In most applications, this parameter will never need to be modified by the user. 4-36 MC68302 USER’S MANUAL MOTOROLA... -

Page 157: Other General Parameters

1. If SCC2 or SCC3 is used, write the parallel port A and B control registers (PACNT and PBCNT) to configure pins as parallel I/O lines or peripheral functions as needed (see 3.3 Parallel I/O Ports). 2. Write SIMODE to configure the serial channels physical interface for the three SCCs MOTOROLA MC68302 USER’S MANUAL 4-37... -

Page 158: Interrupt Mechanism

SCC mask register). The SCC event register is a memory- mapped register that may be read at any time. A bit is cleared by writing a one (writing a zero does not affect a bit's value). 4-38 MC68302 USER’S MANUAL MOTOROLA... -

Page 159: Scc Mask Register (Sccm)

NOTE After power-on reset, when the SCC is enabled for the first time, the SCCE register will show that a change of status occurred, re- MOTOROLA MC68302 USER’S MANUAL 4-39... -

Page 160: Bus Error On Sdma Access

(see 3.2 Interrupt Controller). The interrupt service routine should read the bus error channel number from the parameter RAM at BASE + 67C as follows: 0—SCC1 Tx Channel 1—SCC1 Rx Channel or DRAM Refresh Cycle 2—SCC2 Tx Channel 3—SCC2 Rx Channel 4-40 MC68302 USER’S MANUAL MOTOROLA... -

Page 161: Scc Transparent Mode

• If EXSYN in the BISYNC mode register is set, then the BISYNC controller transfers all characters that follow the external SYNC pulse to the receive buffers. NOTE The BISYNC controller can reverse the bit order in both modes. MOTOROLA MC68302 USER’S MANUAL 4-41... -

Page 162: Disabling The Sccs

Communications Processor (CP) Totally Transparent (Promiscuous) Mode The MC68302 can both receive and transmit the entire serial bit stream transparently. See 4.5.16 Transparent Controller for details. 4.5.10 Disabling the SCCs If an SCC transmitter or receiver is not needed for a period of time or a mode change is re- quired, then it may be disabled and re-enabled later. -

Page 163: Uart Controller

The character format of the UART protocol is shown in Figure 4-17. 7 OR 8 DATA BITS WITH THE LEAST SIGNIFICANT BIT FIRST OPTIONAL START ADDR. PAR. 9/16 TO 2 UART TXD STOP BITS UART TCLK Figure 4-17. UART Frame Format MOTOROLA MC68302 USER’S MANUAL 4-43... - Page 164 TXD line and receives data from the RXD line into memory. The seven dedicated serial interface pins are transmit data (TXD), receive data (RXD), receive clock (RCLK), transmit clock (TCLK), carrier detect (CD), clear to send (CTS), and request to send 4-44 MC68302 USER’S MANUAL MOTOROLA...

-

Page 165: Normal Asynchronous Mode

When a complete character has been clocked in, the contents of the shift register are transferred to the UART receive data register. If there is an error in this character, then the appropriate error bits will be set by the IMP. MOTOROLA MC68302 USER’S MANUAL 4-45... -

Page 166: Asynchronous Ddcmp Mode

When configured to operate in UART mode, the IMP overlays the structure (see Table 4-6) onto the protocol-specific area of that SCC's parameter RAM. Refer to 2.8 MC68302 Mem- ory Map for the placement of the three SCC parameter RAM areas and to Table 4-5 for the other parameter RAM values. - Page 167 In the multidrop mode, the UART controller can provide automatic address recognition of two addresses. In this case, the lower order byte of UADDR1 and UADDR2 are pro- grammed by the user with the two desired addresses. See 4.5.11.6 UART Address Rec- ognition for more details. MOTOROLA MC68302 USER’S MANUAL 4-47...

-

Page 168: Uart Programming Model

Flow-control characters may also be transmitted at any time. In the message-oriented environment, the data stream is divided into buffers. However, the physical format of each character (stop bits, parity, etc.) is not altered. 4-48 MC68302 USER’S MANUAL MOTOROLA... -

Page 169: Uart Command Set

If an enabled receiver has been disabled by clearing ENR in the SCC mode register, the ENTER HUNT MODE command must be given to the channel before setting ENR again. Reception will then begin with the next BD. MOTOROLA MC68302 USER’S MANUAL 4-49... -

Page 170: Uart Address Recognition

SLAVE 3 SCON REGISTER WIRED-OR MODE SELECT TWO 8-BIT ADDRESSES UADDR1 ALLOWS MULTIPLE CAN BE AUTOMATICALLY TRANSMIT PINS TO BE RECOGNIZED IN EITHER UADDR2 DIRECTLY CONNECTED. CONFIGURATION. WOMS Figure 4-18. Two Configurations of UART Multidrop Operation 4-50 MC68302 USER’S MANUAL MOTOROLA... -

Page 171: Uart Control Characters And Flow Control

OFFSET + CHARACTER8 Figure 4-19. UART Control Characters Table CHARACTER7–CHARACTER1—Control Character Value These fields define control characters that should be compared to the incoming character. For 7-bit characters, the eighth bit (bit 7) should be zero. MOTOROLA MC68302 USER’S MANUAL 4-51... - Page 172 The CP clears this bit after transmis- sion. I—Interrupt If set, the M68000 core will be interrupted when this character has been transmitted. (The TX bit will be set in the UART event register.) 4-52 MC68302 USER’S MANUAL MOTOROLA...

-

Page 173: Send Break

If the UART is still in the process of receiving a message that the user has already decided to discard, the message may be aborted by issuing the ENTER HUNT MODE command. The UART receiver will be re-enabled when the message is finished by detecting one idle MOTOROLA MC68302 USER’S MANUAL 4-53... -

Page 174: Uart Error-Handling Procedure

5. Noise Error. Noise error is detected by the UART controller when the three samples taken on every bit are not identical. When this error occurs, the channel writes the re- ceived character to the buffer and proceeds normally but increments the noise error 4-54 MC68302 USER’S MANUAL MOTOROLA... -

Page 175: Fractional Stop Bits

The UART receiver can always receive fractional stop bits. The next character's start bit may begin anytime after the 11th internal clock of the previous character's first stop bit (the UART uses a 16x clock). MOTOROLA MC68302 USER’S MANUAL 4-55... -

Page 176: Uart Mode Register

01 = In the multidrop mode, an additional address/data bit is transmitted with each character. The multidrop asynchronous modes are compatible with the Motorola MC68681 DUART, the Motorola MC68HC11 SCI interface, and the Motorola DSP56000 SCI interface. UM0 is also used to select the wakeup mode before en- abling the receiver or issuing the ENTER HUNT MODE command. -

Page 177: Uart Receive Buffer Descriptor (Rx Bd)

1. Reception of a user-defined control character (when reject (R) bit = 0) 2. Detection of an error during message processing 3. Detection of a full receive buffer 4. Reception of a programmable number of consecutive IDLE characters MOTOROLA MC68302 USER’S MANUAL 4-57... -

Page 178: Figure 4-20. Uart Receive Buffer Descriptor

BD in the table, allowing the user to use fewer than eight BDs to conserve internal RAM. NOTE The user is required to set the wrap bit in one of the first eight BDs; otherwise, errant behavior may occur. 4-58 MC68302 USER’S MANUAL MOTOROLA... -

Page 179: Figure 4-21. Uart Rx Bd Example

32-BIT BUFFER POINTER PROGRESS POINTER (MAX_IDL) (24-BITS USED) WITH THIS BUFFER 10 CHARS 5 CHARS LONG IDLE PERIOD CHARACTERS RECEIVED BY UART PRESENT FOURTH CHARACTER TIME HAS FRAMING ERROR! TIME Figure 4-21. UART Rx BD Example MOTOROLA MC68302 USER’S MANUAL 4-59... - Page 180 A framing error is detected by the UART controller when no stop bit is detected in the re- ceive data string. PR—Parity Error A character with a parity error was received and is located in the last byte of this buffer. OV—Overrun A receiver overrun occurred during message reception. 4-60 MC68302 USER’S MANUAL MOTOROLA...

-

Page 181: Uart Transmit Buffer Descriptor (Tx Bd)

1 = The data buffer, which has been prepared for transmission by the user, has not been transmitted or is currently transmitting. No fields of this BD may be written by the user once this bit is set. MOTOROLA MC68302 USER’S MANUAL 4-61... - Page 182 0 = No preamble sequence is sent. 1 = The UART sends one preamble sequence (9 to 13 ones) before sending the data. The following bits are written by the CP after it has finished transmitting the associated data buffer. 4-62 MC68302 USER’S MANUAL MOTOROLA...

-

Page 183: Uart Event Register

All unmasked bits must be cleared before the CP will clear the internal interrupt request. This register is cleared at reset. An example of the timing of various events in the UART event register is shown in Figure 4- MOTOROLA MC68302 USER’S MANUAL 4-63... -

Page 184: Figure 4-23. Uart Interrupt Events Example

IDL—IDLE Sequence Status Changed A change in the status of the receive serial line was detected on the UART channel. The SCC status register may be read to determine the current status. 4-64 MC68302 USER’S MANUAL MOTOROLA... -

Page 185: Uart Mask Register

(ENT, ENR) bits set. Receive buffers should be linked to the receive buffer table with the interrupt (I) bit set. For simplicity, assume that the line is not multidrop (no addresses are transmitted) and that each S record will fit into a single data buffer. MOTOROLA MC68302 USER’S MANUAL 4-65... -

Page 186: Hdlc Controller

LAPD further di- vides its 16-bit address into different fields to specify various access points within one piece of equipment. It also defines a broadcast address. Some HDLC-type protocols also allow for extended addressing beyond 16-bits. 4-66 MC68302 USER’S MANUAL MOTOROLA... - Page 187 • Separate Interrupts for Frames and Buffers (Receive and Transmit) • Four Address Comparison Registers with Mask • Maintenance of Five 16-Bit Error Counters • Flag/Abort/Idle Generation/Detection • Zero Insertion/Deletion • NRZ/NRZI Data Encoding • 16-Bit or 32-Bit CRC-CCITT Generation/Checking MOTOROLA MC68302 USER’S MANUAL 4-67...

-

Page 188: Hdlc Channel Frame Transmission Processing

When the data buffer has been filled, the HDLC controller clears the empty bit in the BD and generates an interrupt if the interrupt bit in the BD is set. If the incoming frame ex- 4-68 MC68302 USER’S MANUAL MOTOROLA... -

Page 189: Hdlc Memory Map

When configured to operate in HDLC mode, the IMP overlays the structure shown in Table 4-7 onto the protocol-specific area of that SCC parameter RAM. Refer to 2.8 MC68302 Memory Map for the placement of the three SCC parameter RAM areas and to Table 4-2 for the other parameter RAM values. -

Page 190: Hdlc Command Set

BD (TBD#) in the channel's transmit BD table. If the transmitter is being re-enabled, the RESTART TRANSMIT command must be used and should be followed by the enabling of the transmitter in the SCC mode register. 4-70 MC68302 USER’S MANUAL MOTOROLA... -

Page 191: Hdlc Address Recognition

HDLC frame is discarded, and the LG (Rx frame too long) bit is set in the last BD belonging to that frame. The HDLC controller waits to the end of the frame and reports the frame status MOTOROLA MC68302 USER’S MANUAL 4-71... -

Page 192: Hdlc Error-Handling Procedure

BD of length two will be opened to report the overrun, and the RXB interrupt will be generated (if enabled). 2. Carrier Detect Lost During Frame Reception. When this error occurs and the channel 4-72 MC68302 USER’S MANUAL MOTOROLA... -

Page 193: Hdlc Mode Register

RETRC—Frame Retransmission Counter (due to collision) 4.5.12.9 HDLC Mode Register Each SCC mode register is a 16-bit, memory-mapped, read-write register that controls the SCC operation. The term HDLC mode register refers to the protocol-specific bits (15–6) of MOTOROLA MC68302 USER’S MANUAL 4-73... - Page 194 This bit may be dynamically modified. If toggled from a one to a zero between frames, a maximum of two additional flags will be transmitted before the idle condition will begin. Toggling FLG will never result in partial flags being transmitted. 4-74 MC68302 USER’S MANUAL MOTOROLA...

-

Page 195: Hdlc Receive Buffer Descriptor (Rx Bd)

HDLC controller is currently filling the buffer with received data. X—External Buffer 0 = The buffer associated with this BD is in internal dual-port RAM. 1 = The buffer associated with this BD is in external memory. MOTOROLA MC68302 USER’S MANUAL 4-75... -

Page 196: Figure 4-27. Hdlc Receive Bd Example

PRESENT UNEXPECTED ABORT TIME OCCURS BEFORE TIME CLOSING FLAG! LEGEND: F = FLAG I = INFORMATION BYTE A = ADDRESS BYTE CR = CRC BYTE C = CONTROL BYTE Figure 4-27. HDLC Receive BD Example 4-76 MC68302 USER’S MANUAL MOTOROLA... - Page 197 BD. NO—Rx Nonoctet Aligned Frame A frame that contained a number of bits not exactly divisible by eight was received. AB—Rx Abort Sequence A minimum of seven consecutive ones was received during frame reception. MOTOROLA MC68302 USER’S MANUAL 4-77...

-

Page 198: Hdlc Transmit Buffer Descriptor (Tx Bd)

— — — — — — — — OFFSET + 2 OFFSET + 4 DATA LENGTHTX BUFFER POINTER (24-bits used, upper 8 bits must be 0) OFFSET + 6 Figure 4-28. HDLC Transmit Buffer Descriptor 4-78 MC68302 USER’S MANUAL MOTOROLA... - Page 199 1 = Transmit the CRC sequence after the last data byte. Bits 9–2—Reserved for future use. The following status bits are written by the HDLC controller after it has finished transmitting the associated data buffer. MOTOROLA MC68302 USER’S MANUAL 4-79...

-

Page 200: Hdlc Event Register

All unmasked bits must be cleared before the CP will clear the internal interrupt request. This register is cleared at reset. An example of the timing of various events in the HDLC event register is shown in Figure 4- 4-80 MC68302 USER’S MANUAL MOTOROLA... -

Page 201: Figure 4-29. Hdlc Interrupt Events Example

CD—Carrier Detect Status Changed A change in the status of the CD line was detected on the HDLC channel. The SCC status register may be read to determine the current status. MOTOROLA MC68302 USER’S MANUAL 4-81... -

Page 202: Hdlc Mask Register

Each class of frame starts with a standard two octet synchroni- zation pattern and ends with a block check code (BCC). The end of text character (ETX) is used to separate the text and BCC fields. 4-82 MC68302 USER’S MANUAL MOTOROLA... -

Page 203: Figure 4-30. Typical Bisync Frames

The BISYNC controller consists of separate transmit and receive sections whose operations are asynchronous with the M68000 core and may be either synchronous or asynchronous with respect to the other SCCs. Each clock can be supplied from either the internal baud MOTOROLA MC68302 USER’S MANUAL 4-83... -

Page 204: Bisync Channel Frame Transmission Processing

SYN1–SYN2 pair followed by either SYNCs or idles according to the SYNF bit in the BISYNC mode register. This case is an underrun error and is described further in 4.5.13.8 BISYNC Error-Handling Procedure. 4-84 MC68302 USER’S MANUAL MOTOROLA... -

Page 205: Bisync Channel Frame Reception Processing

See 4.5.16 Transparent Controller. 4.5.13.3 Bisync Memory Map When configured to operate in BISYNC mode, the IMP overlays the structure listed in Table 4-8 onto the protocol-specific area of that SCC parameter RAM. Refer to 2.8 MC68302 MOTOROLA MC68302 USER’S MANUAL... -

Page 206: Bisync Command Set

TBD# is not advanced. SYNC characters consisting of SYNC-SYNC or DLE-SYNC pairs (according to the transmitter mode) will be continually transmitted until transmission is re- enabled by issuing the RESTART TRANSMIT command. The STOP TRANSMIT com- 4-86 MC68302 USER’S MANUAL MOTOROLA... -

Page 207: Bisync Control Character Recognition

DMA-oriented environment. Their main use is for receive buff- ers longer than one byte. In single-byte buffers, each byte can easily be inspected, and con- trol character recognition should be disabled. MOTOROLA MC68302 USER’S MANUAL 4-87... -

Page 208: Figure 4-31. Bisync Control Characters Table

E—End of Table 0 = This entry is valid. The lower eight bits will be checked against the incoming char- acter. 1 = The entry is not valid. No valid entries exist beyond this entry. 4-88 MC68302 USER’S MANUAL MOTOROLA... -

Page 209: Bsync-Bisync Sync Register

When the BISYNC receiver is in transparent mode and a DLE character is received, the re- ceiver discards this character and excludes it from the BCS if the valid (V) bit is set. If the second (next) character is a SYNC character, the BISYNC controller discards it and ex- MOTOROLA MC68302 USER’S MANUAL 4-89... -

Page 210: Bisync Error-Handling Procedure

RX interrupt (if enabled). This error is the highest priority; the rest of the message is lost and no other errors are checked in the message. The receiver then enters hunt mode immediately. 3. Parity Error. When this error occurs, the channel writes the received character to the 4-90 MC68302 USER’S MANUAL MOTOROLA... -

Page 211: Bisync Mode Register

L1SY1 pin. In PCM mode, the L1SY1–L1SY0 pins are used. In NMSI mode, the CD pins (and the CD timing) are used to synchronize the data. CD should be asserted on the second data bit of the frame when used as a sync. MOTOROLA MC68302 USER’S MANUAL 4-91... - Page 212 The BISYNC receiver internally stores two BCS calculations with a byte delay (eight serial clocks) between them. This enables the user to examine a received data byte and then decide whether or not it should be part of the BCS calculation. This is useful when control 4-92 MC68302 USER’S MANUAL MOTOROLA...

-

Page 213: Bisync Receive Buffer Descriptor (Rx Bd)

BD. 1 = The data buffer associated with this BD is empty. This bit signifies that the BD and its associated buffer are available to the CP. After it sets this bit, the M68000 core MOTOROLA MC68302 USER’S MANUAL 4-93... - Page 214 While in transparent mode, a DLE character was received, and the next character was not DLE, SYNC, or a valid entry in the control characters table. PR—Parity Error A character with a parity error was received and is the last byte of this buffer. 4-94 MC68302 USER’S MANUAL MOTOROLA...

-

Page 215: Bisync Transmit Buffer Descriptor (Tx Bd)

Figure 4-33. BISYNC Transmit Buffer Descriptor The first word of the Tx BD contains status and control bits. These bits are prepared by the user before transmission and are set by the CP after the buffer has been transmitted. MOTOROLA MC68302 USER’S MANUAL 4-95... - Page 216 1 = Buffer consists of characters to be included in the BCS accumulation. BR—BCS Reset 0 = The BCS accumulation is not reset. 1 = The transmitter BCS accumulation is reset (used for STX or SOH) before sending the data buffer. 4-96 MC68302 USER’S MANUAL MOTOROLA...

-

Page 217: Bisync Event Register

4.5.13.12 BISYNC Event Register The SCC event register (SCCE) is referred to as the BISYNC event register when the SCC is programmed as a BISYNC controller. It is an 8-bit register used to report events recog- MOTOROLA MC68302 USER’S MANUAL 4-97... -

Page 218: Bisync Mask Register

BISYNC event register. If a bit in the BISYNC mask register is a one, the cor- responding interrupt in the event register will be enabled. If the bit is zero, the corresponding interrupt in the event register will be masked. This register is cleared upon reset. 4-98 MC68302 USER’S MANUAL MOTOROLA... -

Page 219: Programming The Bisync Controllers

Control Characters Next Entry After the end of text (ETX), a BCS is expected; then the buffer should be closed. Hunt mode should be entered when line turnaround occurs. ENQ characters are used to abort transmis- MOTOROLA MC68302 USER’S MANUAL 4-99... -

Page 220: Ddcmp Controller

Asynchronous DDCMP frames are composed of asynchronous UART characters, which together form the frame. The receiver and transmit- ter clocks are not linked; the receiver resynchronizes itself every byte using the start and stop bits of each UART character. 4-100 MC68302 USER’S MANUAL MOTOROLA... -

Page 221: Ddcmp Channel Frame Transmission Processing

(BD) in the channel's transmit BD table. When there is a message to transmit, the DDCMP controller fetches the data from memory and starts transmitting the message (after first transmitting the SYN1–SYN2 pair when the link is synchronous). MOTOROLA MC68302 USER’S MANUAL 4-101... -

Page 222: Ddcmp Channel Frame Reception Processing

SYN1–SYN2 fields of the data synchronization register (see 4.5.4 SCC Data Synchroniza- tion Register (DSR)). If the two are not equal, the next bit is shifted in, and the comparison is repeated. When the registers match, hunt mode is terminated, and character assembly 4-102 MC68302 USER’S MANUAL MOTOROLA... -

Page 223: Ddcmp Memory Map

When configured to operate in DDCMP mode, the IMP overlays the structure illustrated in Table 4-9 onto the protocol-specific area of that SCC's parameter RAM. Refer to 2.8 MC68302 Memory Map for the placement of the three SCC parameter RAM areas and to Table 4-5 for the other parameter RAM values. -

Page 224: Ddcmp Programming Model

BD in the table approximately every eight transmit clocks. The channel STOP TRANSMIT command disables the transmission of messages on the transmit channel. If this command is received by the DDCMP controller during message 4-104 MC68302 USER’S MANUAL MOTOROLA... -

Page 225: Ddcmp Control Character Recognition

The 8-bit DSYN1 register should be written with the same value that was written in the SYN1 byte of the data synchronization register (DSR). DSYN1 is a memory-mapped read-write register. NOTE For correct operation of DDCMP, DSYN1, SYN1, and SYN2 must be the same value. MOTOROLA MC68302 USER’S MANUAL 4-105... -

Page 226: Ddcmp Address Recognition

(UN) bit in the BD, and generates the trans- mit error (TXE) interrupt (if enabled). The channel will resume transmission after the reception of the RESTART TRANSMIT command. The FIFO size is three bytes. 4-106 MC68302 USER’S MANUAL MOTOROLA... - Page 227 (FR) bit in the BD, and generates the RBK interrupt (if enabled). When this error occurs, parity is not checked for this character. MOTOROLA MC68302 USER’S MANUAL 4-107...

-

Page 228: Ddcmp Mode Register

If NOS3–NOS0 = 0000, then 1 SYNC pair will be transmitted; if NOS3–NOS0 = 1111, then 16 SYNC pairs will be transmitted. NOTE With appropriate programming of the transmit BD (TC = 1 and L = 0), it is possible to transmit back-to-back messages. 4-108 MC68302 USER’S MANUAL MOTOROLA... -

Page 229: Ddcmp Receive Buffer Descriptor (Rx Bd)

The first word of the Rx BD contains control and status bits. Bits 15–12 are written by the user before the buffer is linked to the Rx BD table, and bits 5–0 and 11–8 are set by the IMP MOTOROLA MC68302 USER’S MANUAL 4-109... - Page 230 1 = The buffer contains a message header. NOTE To correctly identify buffers containing headers, the buffer size should be eight or more bytes in length so that the header will fit in a single buffer. 4-110 MC68302 USER’S MANUAL MOTOROLA...

- Page 231 It is written by the CP once as the BD is closed. NOTE The actual buffer size should be greater than or equal to eight (to ensure the header is received in one buffer). MOTOROLA MC68302 USER’S MANUAL 4-111...

-

Page 232: Ddcmp Transmit Buffer Descriptor (Tx Bd)

1 = This is the last BD in the Tx BD table. After this buffer has been used, the DDCMP controller will transmit data from the first BD in the table. NOTE The user is required to set the wrap bit in one of the first eight BDs; otherwise, errant behavior may occur. 4-112 MC68302 USER’S MANUAL MOTOROLA... - Page 233 The DDCMP controller encountered a transmitter underrun condition while transmitting the associated data buffer. NOTE This error can occur only on synchronous links. CT—CTS Lost CTS in NMSI mode or grant in IDL/GCI mode was lost during message transmission. MOTOROLA MC68302 USER’S MANUAL 4-113...

-

Page 234: Ddcmp Event Register

A complete block has been received on the DDCMP channel. A block is defined as recep- tion of a complete header, a complete message, or a receiver error condition. BSY—Busy Condition A data byte was received and discarded due to lack of buffers. The receiver will enter hunt mode automatically. 4-114 MC68302 USER’S MANUAL MOTOROLA... -

Page 235: Ddcmp Mask Register

Another rate adaption protocol, called V.120, is an alternative protocol to V.110. V.120 is an extension of the LAPD protocol and may be implemented on the MC68302 using an SCC configured in HDLC mode. -

Page 236: Bit Rate Adaption Of Synchronous Data Signaling Rates Up To 19.2 Kbps

V.110 operation (see 4.5.9 SCC Transparent Mode). The M68000 core will need to format the framing pattern in the 48-kbps conversion case. For the 56-kbps rate conversion, however, the B channel mask (SIMASK) in the serial channel physical interface can be used. 4-116 MC68302 USER’S MANUAL MOTOROLA... -

Page 237: Adaption For Asynchronous Rates Up To 19.2 Kbps

Another SCC controller may be used to receive data from the R interface. The M68000 core should then format the data according to the V.110 protocol to create the V.110 80-bit frame data buffer. The V.110 controller will then transmit it onto the B channel. MOTOROLA MC68302 USER’S MANUAL 4-117... -

Page 238: Programming Model

• Receiving of 10 bytes (80-bit frame) • Detecting of an error • Issuing the ENTER HUNT MODE command 4-118 MC68302 USER’S MANUAL MOTOROLA... -

Page 239: Figure 4-40. V.110 Receive Buffer Descriptor

A frame with a synchronization error was received. A synchronization error is detected by the V.110 controller when the MSB of a byte (except the all-zeros byte) is not one. OV—Overrun A receiver overrun occurred during message reception. MOTOROLA MC68302 USER’S MANUAL 4-119... -

Page 240: Transmit Buffer Descriptor (Tx Bd)

No fields of this BD may be written by the user once this bit is set. X—External Buffer 0 = The buffer associated with this BD is in internal dual-port RAM. 1 = The buffer associated with this BD is in external memory. 4-120 MC68302 USER’S MANUAL MOTOROLA... -

Page 241: Event Register

The SCC event register (SCCE) is referred to as the V.110 event register when the SCC is configured as a V.110 controller. It is an 8-bit register used to report events recognized by the V.110 channel and to generate interrupts. On recognition of an event, the V.110 control- MOTOROLA MC68302 USER’S MANUAL 4-121... -

Page 242: Mask Register